IDF Fall 2006 - Day 2: Opteron vs. Xeon, SSE4 & Intel's Torrenza competitor Announced

by Anand Shimpi & Virginia Lee on September 27, 2006 1:12 PM EST- Posted in

- Trade Shows

Intel Follows AMD's Lead, Again: Cloning Torrenza

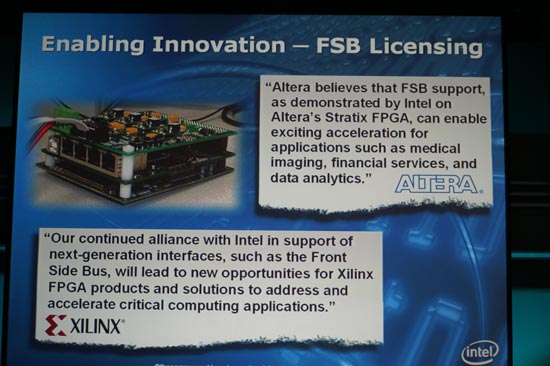

In another example of a string of Intel following AMD's lead, Gelsinger announced extending Intel's FSB license to FPGA manufacturers like Xilinx so that companies can produce other chips that can work alongside Intel processors with a direct FSB connection to the MCH. This should sound a lot like a less elegant implementation of AMD's Torrenza initiative; as you may remember, Torrenza is the platform standard that AMD introduced to allow other, non-AMD processors (or accelerators) to be installed in standard Opteron sockets through licensing and use of the coherent Hyper Transport specification. Intel's FSB licensing will also allow various accelerators to be plugged into a high bandwidth, low latency (potentially cache coherent) bus that would connect directly to the MCH in an Intel system.

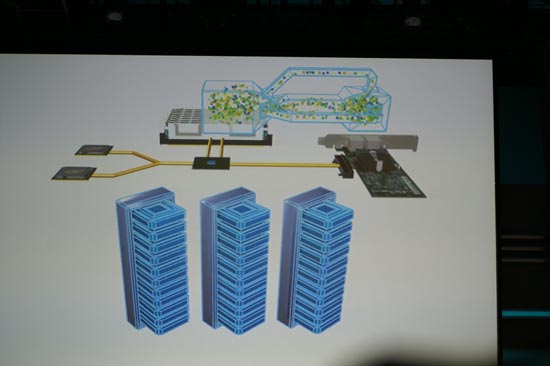

This device somehow implements Intel's FSB license

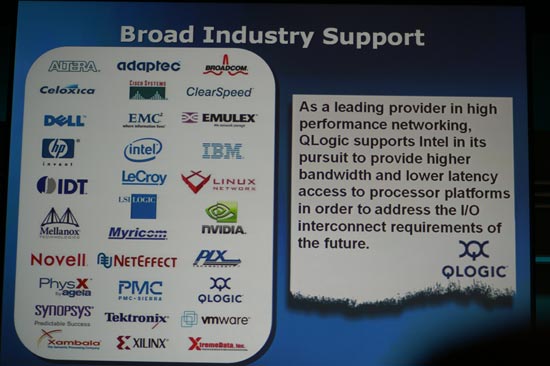

Intel also announced work with IBM to create an extension to PCI Express, codenamed Geneseo that would be used as a higher bandwidth, lower latency interface for everything from graphics cards to physics accelerators. Gelsinger threw up a slide that showcased the broad industry support for creating products that would work with the Geneseo interface. Notable members of the alliance are NVIDIA and AGEIA for its PhysX card, indicating that Intel's thinking is similar to AMD's in that there could be a future for physics accelerator cards or even a higher speed, lower latency interconnect for GPUs that would utilize this interface. Note the absence of ATI from the list of partners supporting Intel's efforts.

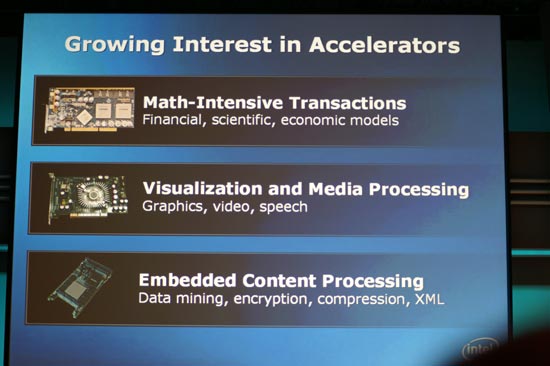

Effectively, what Intel is hoping to do is gain momentum and industry support for an alternative to AMD's Hyper Transport for use with various 3rd party accelerator cards. Since Intel is unlikely to embrace Hyper Transport and AMD's Torrenza's initiative, simply extending PCI Express with additional focus on creating a higher bandwidth, lower latency version of the bus for these accelerator cards with the help of the rest of the industry (except AMD) is the next best option.

Intel expects to iron out a specification in the next 1 - 1.5 years, and the first products will be available in the coming years after that. Obviously, AMD has a much larger head start in this area and we're interested to see how things pan out given AMD's timing advantage and industry support for Hyper Transport.

IBM came on stage to talk about some of the things Intel and IBM focused on in developing the spec for the new Geneseo interface spec for 3rd party accelerators to communicate directly with the MCH in a system. The information that was shared was vague at best, but the animations during the presentation give you an example of a usage model Intel is looking at with its Torrenza-like platform approach.

Based on the vague comments by IBM, it looks like these accelerators running over the Geneseo interface could be cache coherent, support reordering of memory requests in order to prioritize the most important requests and able to be power managed must like any other component in the system.

18 Comments

View All Comments

archikins - Wednesday, September 27, 2006 - link

..not much information in your article about this except the "i hate amd" screen shot. Could you please add some more info on this?AnnihilatorX - Wednesday, September 27, 2006 - link

What's with the "I hate amd" password...JarredWalton - Wednesday, September 27, 2006 - link

It was a joke more than anything - that was his "secret" password, but he got "hacked".tygrus - Thursday, September 28, 2006 - link

Was he blaming AMD that he was hacked? Implying that if it was an Intel machine with ??? tech it wouldn't.A real reason to hate AMD would be if AMD could beat Intel. Why would you hate someone you had beat ? Freudian slip that Intel thinks AMD can beat Intel ?

Who's afraid of the big bad wolf :)

slashbinslashbash - Wednesday, September 27, 2006 - link

So we've got IBM at IDF saying that they're supporting Intel in this new venture to plug accelerator chips into the motherboard with cache coherency and all kinds of really big stuff, and no explicit mention of Cell?wien - Wednesday, September 27, 2006 - link

Hmm. What's going on with the ads recently? When I open this page in Firefox/Epiphany on Linux, I'm instantly redirected to Newegg, Zipzoomfly or some other advertiser. Opera at least opens a new tab for the ad, but it's still mighty annoying.slatr - Wednesday, September 27, 2006 - link

This makes me want to work for Intel. I am such a nerd.psychobriggsy - Wednesday, September 27, 2006 - link

"Socket-F Opteron 285"No such beast exists. It'd be a 2220 or something. Either the box was Socket F and they got the name wrong, or it was Socket 940 still.

Intel's bus licensing thing looks quite weak compared to AMD's Torrenza. Intel have more might however, but a potential 18 months to mere specification isn't a good start. Quite what advantages they'll have over HyperTransport 3 remains to be seen, but if it is competing just to be awkward then Intel haven't really matured as a company like many had hoped.

Hopefully the benchmarking suite will be non-biased and based around sensible usage patterns. I guess we'll see soon enough.

The new instructions will be useful if they accellerate common algorithms decently over software implementations, e.g., CRC32 was on the list. However are these sensible instructions to have? Would general purpose accellerators, e.g., TCP/IP and Encryption, be better?

finalfan - Wednesday, September 27, 2006 - link

The one advantage of fsb bus licensing is it makes the 3rd party device being able to access system memory without forcing its own memory controller and its own memory since it is connected with MCH and MCH will be able to ensure memory coherence. It makes the other devices more like a CPU than a co-processor.Kiijibari - Wednesday, September 27, 2006 - link

Nobody forces a memory controller with torrenza. It is jsut optional. Some dual Opteron mainboards also just use 1 CPU's memory, the other CPU is accesing the RAM through the coherent Hypertransport bus.Thus the AMD solution is more flexible.

cheers

Kiijibari

P.S: @anandtech, good article :)