IDF Fall 2006 - Day 2: Opteron vs. Xeon, SSE4 & Intel's Torrenza competitor Announced

by Anand Shimpi & Virginia Lee on September 27, 2006 1:12 PM EST- Posted in

- Trade Shows

Intel Announces new Instructions for 45nm, SSE4 and more

Unexpectedly, Gelsinger announced the 50 new instructions that will be present in its upcoming 45nm processors (Penryn and Nehalem) - it's "SSE4 and more".

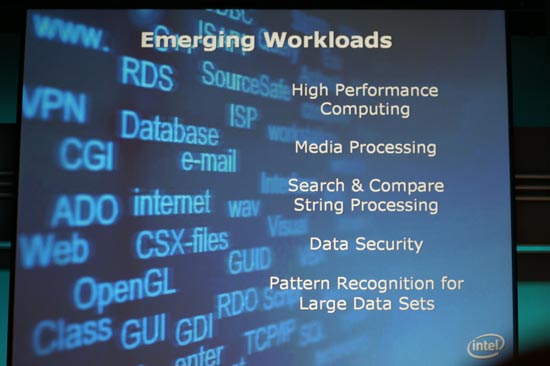

These are some of the workloads the new instructions will help accelerate

Today Intel will be publishing a white paper detailing the new instructions and as they get implemented in silicon, Intel will disclose more information about the instructions.

Intel's approach to SSE4 disclosure is a significant departure from how previous x86 instruction extensions have been disclosed by the company. It's another example of Intel's more open and friendly approach to its upcoming roadmaps; we're hoping Intel will only continue to be more open with its future plans, and we do have AMD to thank for keeping the pressure on Intel to bring about such a dramatic change in behavior.

18 Comments

View All Comments

archikins - Wednesday, September 27, 2006 - link

..not much information in your article about this except the "i hate amd" screen shot. Could you please add some more info on this?AnnihilatorX - Wednesday, September 27, 2006 - link

What's with the "I hate amd" password...JarredWalton - Wednesday, September 27, 2006 - link

It was a joke more than anything - that was his "secret" password, but he got "hacked".tygrus - Thursday, September 28, 2006 - link

Was he blaming AMD that he was hacked? Implying that if it was an Intel machine with ??? tech it wouldn't.A real reason to hate AMD would be if AMD could beat Intel. Why would you hate someone you had beat ? Freudian slip that Intel thinks AMD can beat Intel ?

Who's afraid of the big bad wolf :)

slashbinslashbash - Wednesday, September 27, 2006 - link

So we've got IBM at IDF saying that they're supporting Intel in this new venture to plug accelerator chips into the motherboard with cache coherency and all kinds of really big stuff, and no explicit mention of Cell?wien - Wednesday, September 27, 2006 - link

Hmm. What's going on with the ads recently? When I open this page in Firefox/Epiphany on Linux, I'm instantly redirected to Newegg, Zipzoomfly or some other advertiser. Opera at least opens a new tab for the ad, but it's still mighty annoying.slatr - Wednesday, September 27, 2006 - link

This makes me want to work for Intel. I am such a nerd.psychobriggsy - Wednesday, September 27, 2006 - link

"Socket-F Opteron 285"No such beast exists. It'd be a 2220 or something. Either the box was Socket F and they got the name wrong, or it was Socket 940 still.

Intel's bus licensing thing looks quite weak compared to AMD's Torrenza. Intel have more might however, but a potential 18 months to mere specification isn't a good start. Quite what advantages they'll have over HyperTransport 3 remains to be seen, but if it is competing just to be awkward then Intel haven't really matured as a company like many had hoped.

Hopefully the benchmarking suite will be non-biased and based around sensible usage patterns. I guess we'll see soon enough.

The new instructions will be useful if they accellerate common algorithms decently over software implementations, e.g., CRC32 was on the list. However are these sensible instructions to have? Would general purpose accellerators, e.g., TCP/IP and Encryption, be better?

finalfan - Wednesday, September 27, 2006 - link

The one advantage of fsb bus licensing is it makes the 3rd party device being able to access system memory without forcing its own memory controller and its own memory since it is connected with MCH and MCH will be able to ensure memory coherence. It makes the other devices more like a CPU than a co-processor.Kiijibari - Wednesday, September 27, 2006 - link

Nobody forces a memory controller with torrenza. It is jsut optional. Some dual Opteron mainboards also just use 1 CPU's memory, the other CPU is accesing the RAM through the coherent Hypertransport bus.Thus the AMD solution is more flexible.

cheers

Kiijibari

P.S: @anandtech, good article :)