AMD Announces Radeon RDNA 3 GPU Livestream Event for November 3rd

by Ryan Smith on October 20, 2022 11:00 AM EST

Following on the heels of AMD’s CPU-centric event back in August, AMD today has sent out a press release announcing that they will be holding a similar event in November for their Radeon consumer graphics business. Dubbed “together we advance_gaming”, the presentation is slated to be all about AMD Radeon, with a focus on the upcoming RDNA 3 graphics architecture and all the performance and power efficiency benefits it will bring. The event is set to kick off on November 3rd at 1pm PT (20:00 UTC), with undisclosed AMD executives presenting details.

Like the Ryzen event in August, next month’s Radeon event appears to be AMD gearing up for the launch of its next generation of consumer products – this time on the GPU side of matters. Back at the start of the summer, AMD confirmed that RDNA 3 architecture products were scheduled to arrive this year, so we have been eagerly awaiting the arrival of AMD’s next generation of video cards.

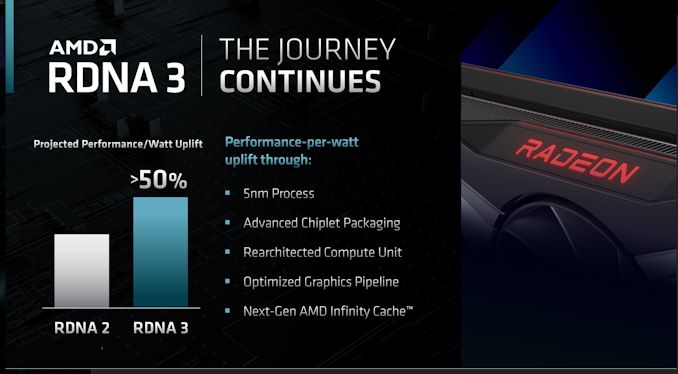

Though unlike AMD’s CPU efforts, the company has been far more mum about its next-gen GPU efforts. So details in advance on what will presumably be the Radeon RX 7000 series have been limited. The biggest items disclosed thus far are that AMD is targeting another 50% increase in performance-per-watt, and that these new GPUs (Navi 3x) will be made on a 5nm process (undoubtedly TSMC’s). Past that, AMD hasn’t given any guidance on what to expect for performance.

One interesting aspect, however, is that AMD has confirmed that they will be employing chiplets with this generation of products. To what extent, and whether that’s on all parts or just some, remains to be seen. But chiplets are in some respects the holy grail of GPU construction, because they give GPU designers options for scaling up GPUs past today’s die size (reticle) and yield limits. That said, it’s also a holy grail because the immense amount of data that must be passed between different parts of a GPU (on the order of terabytes per second) is very hard to do – and very necessary to do if you want a multi-chip GPU to be able to present itself as a single device.

We’re also apparently in store for some more significant upgrades to AMD’s overall GPU architecture. Though what exactly a “rearchitected compute unit” and “optimized graphics pipeline” fully entail remains to be seen.

Thankfully we should have our answer here in two weeks. The presentation is slated to air on November 3rd at 1pm Pacific, on AMD’s YouTube channel. And of course, be sure to check out AnandTech for a full rundown and analysis of AMD’s announcements.

Source: AMD

17 Comments

View All Comments

Mr Perfect - Thursday, October 20, 2022 - link

Personally, this is the launch I'm watching. Arc was 2020 midrange and RTX 4000 is expensive and power hungry, so a 2022 high end card with an eye on power is tempting.Any chance Anandtech will be reviewing them?

Ryan Smith - Thursday, October 20, 2022 - link

TBDsaylick - Thursday, October 20, 2022 - link

Ryan, I think you have a typo at the end of the article. You wrote that the presentation is slated to air on Nov 29th, but it clearly is for Nov 3rd. Also, do you think you will have a GPU review this time? :)Mr Perfect - Thursday, October 20, 2022 - link

Fair enough. Hopefully your staffing issues get sorted out, because your GPU articles are sorely missed.PeachNCream - Wednesday, October 26, 2022 - link

I would actually agree. Modern video-based reviews are not as effective at presenting the expected graphs and charts that benchmark-heavy scenarios like these present. Though if all else fails, Tom's Hardware is owned by the same company and likely will have a review. It also has some ex-AT staff so if were a fan of someone, you might find their familiar typos not to far away.kpb321 - Thursday, October 20, 2022 - link

It will be interesting to see what they do here with chiplets. Looking at the 6000 series you could make the base 6400/6500 a single chiplet with a 64bit memory bus. Then the 6600 would be 2 chiplets, the 6700's would be 3 chiplets and the 6800/6900 would be 4 chiplets. That would pretty much line up the memory bus scaling but not quite the compute units or cache. I'm not sure if you could present 4 chiplets with a PCI-E 4x link as a single PCI-E 16x device or if a 12x PCI-E link is even valid. A Central IO die with the PCI-E link, infinity cache and the video encode/decode blocks could make a lot of sense too. You'd avoid having 2 or 3 unused chiplet links on the base card and the possibility of non-uniform access if you had 2 hops to memory/cache on another chiplet.They could also only use the chiplets in the highest tier or two keeping more of the low/mid range cards using single chips. Maybe the 7500 is single chip with no multi chip support. 7600 is single chip with multi chip support and then 7700 is two partially enabled 7600 and the 7800/7900 are two 7600's.

Either way it will be interesting to see how they pull it off and how they keep the power costs manageable for the high bandwidth interconnects between the chiplets.

Mr Perfect - Thursday, October 20, 2022 - link

The rumor mill has us covered on this one, assuming their sources are correct of course.The biggest Navi31 is rumored to be a large graphics die with six smaller memory dies clustered around it. Mid-sized Navi32 should be a mid sized graphics die surrounded by four memory dies. The smallest die, Navi33, is still monolithic.

https://videocardz.com/newz/amd-navi-3x-gpus-expos...

MooseMuffin - Thursday, October 20, 2022 - link

I wonder which cards they'll choose to launch. Nvidia has clearly decided they want to sell through their inventory of the 3xxx cards and only launched their 4xxx cards at the highest end that the older cards can't reach. Presumably AMD is in a similar situation with last gen inventory, but they do have an opening if the new stuff resets the price/performance curve.webdoctors - Thursday, October 20, 2022 - link

I think you'll be dissapointed on the price/perf curve. Looking at the MSRP for AMD CPUs for price/transistor, its unlikely the GPUs which are 10X the transistor count will be much less than 10X the cost. Fab space is limited and I'd imagine they'd want to push fabbing CPUs that make them much more money over costly GPUs.With the quality and demand of their CPUs, might make sense to have very limited run of GPUs until fab pricing comes down.

mcnabney - Thursday, October 27, 2022 - link

Don't count transistors (and that 10x is wrong).Navi 31 is using the cheaper N6 process. Total die size is under 350mm^2, which is going to save them a ton of money. Navi 33 is monolithic and is around 200mm^2. Don't worry about the GPU production. If there is any limit it will be GDDR6 availability. There won't even be any real crippled-core binning. Only binning for chiplets that can clock higher for selling MCDs that go into hot-clocked boards with their partners (or RX 7900/7950).

If they have low volume of RX6XXX boards in the channel they can undercut Nvidia by both price and power demand which can drive up their market share (they already own the consoles). Nvidia's 12pin connector on their 40 series is not well timed for the green team.