Update: PCI Express 6.0 Draft 0.71 Released, Final Release by End of Year

by Ryan Smith on July 2, 2021 7:00 AM EST- Posted in

- CPUs

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

Update 07/02: Albeit a couple of days later than expected, the PCI-SIG has announced this morning that the PCI Express draft 0.71 specification has been released for member review. Following a minimum 30 day review process, the group will be able to publish the draft 0.9 version of the specficiation, putting them on schedule to release the final version of the spec this year.

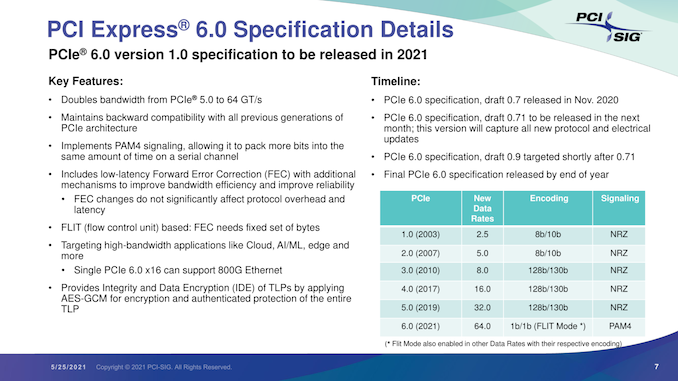

Originally Published 05/25

As part of their yearly developer conference, the PCI Special Interest Group (PCI-SIG) also held their annual press briefing today, offering an update on the state of the organization and its standards. The star of the show, of course, was PCI Express 6.0, the upcoming update to the bus standard that will once again double its data transfer rate. PCI-SIG has been working on PCIe 6.0 for a couple of years now, and in a brief update, confirmed that the group remains on track to release the final version of the specification by the end of this year.

The most recent draft version of the specification, 0.7, was released back in November. Since then, PCI-SIG has remained at work collecting feedback from its members, and is gearing up to release another draft update next month. That draft will incorporate the all of the new protocol and electrical updates that have been approved for the spec since 0.7.

In a bit of a departure from the usual workflow for the group, however, this upcoming draft will be 0.71, meaning that PCIe 6.0 will be remaining at draft 0.7x status for a little while longer. The substance of this decision being that the group is essentially going to hold for another round of review and testing before finally clearing the spec to move on to the next major draft. Overall, the group’s rules call for a 30-day review period for the 0.71 draft, after which the group will be able to release the final draft 0.9 specification.

Ultimately, all of this is to say that PCIe 6.0 remains on track for its previously-scheduled 2021 release. After draft 0.9 lands, there will be a further two-month review for any final issues (primarily legal), and, assuming the standard clears that check, PCI-SIG will be able to issue the final, 1.0 version of the PCIe 6.0 specification.

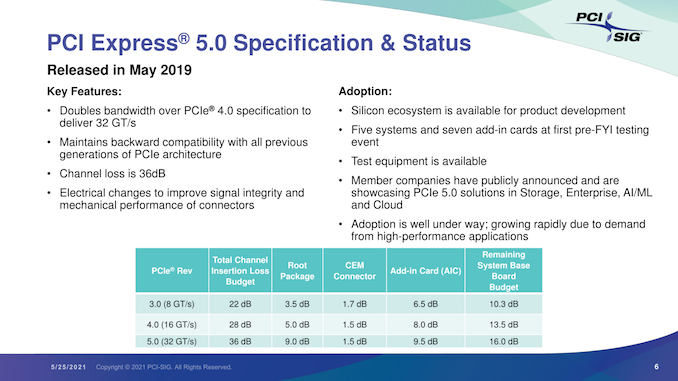

In the interim, the 0.9 specification is likely to be the most interesting from a technical perspective. Once the updated electrical and protocol specs are approved, the group will be able to give some clearer guidance on the signal integrity requirements for PCIe 6.0. All told we’re not expecting much different from 5.0 (in other words, only a slot or two on most consumer motherboards), but as each successive generation ratchets up the signaling rate, the signal integrity requirements have tightened.

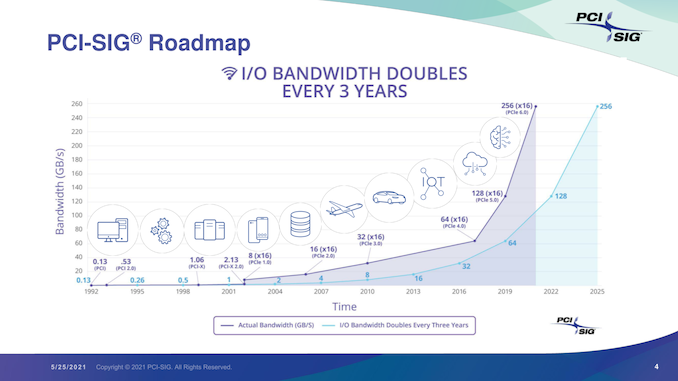

Overall, the unabashedly nerdy standards group is excited about the 6.0 standard, comparing it in significance to the big jump from PCIe 2.0 to PCIe 3.0. Besides proving that they’re once again able to double the bandwidth of the ubiquitous bus, it will mean that they’ve been able to keep to their goal of a three-year cadence. Meanwhile, as the PCIe 6.0 specification reaches completion, we should finally begin seeing the first PCIe 5.0 devices show up in the enterprise market.

103 Comments

View All Comments

Yojimbo - Tuesday, May 25, 2021 - link

I'm always bothered by seeing that PCI-SIG doubling graph. Starting the graph back at PCI in 1992 glosses over that PCI was too slow to begin with, which is why there was VESA local bus, and then AGP (Intel), and then finally the development of 3GIO by Intel, Dell, HP, and IBM, which was handed over to the PCI-SIG and renamed PCI-Express.The graph should start with PCIe 1.0 in 2003. Then doubling every 3 years from there would get us on time to the speed that PCIe 6.0 achieves in 2021 - not the 4 years later interpretation they show starting from 1992 that relies on the work of outside groups that created their own specification to get around PCI-SIG - providing we ignore the fact that PCIe 1.0 devices were available in 2004, a year after the specification release, and it's now 2021, two years after the PCIe 5.0 spec release, and we still don't have access to PCIe 5.0 devices. Since PCIe 6.0 and PCIe 5.0 are unlikely to appear at almost same time I don't think we'll be getting access to PCIe 6.0 speeds next year.

cosmotic - Tuesday, May 25, 2021 - link

We barely have access to PCIe 4 devices.DigitalFreak - Tuesday, May 25, 2021 - link

PCIe 5.0 and 6.0 are only really useful in servers and high end workstation environments, where high speed networking or GPU interconnects are needed.FatFlatulentGit - Tuesday, May 25, 2021 - link

I could see 5.0 and 6.0 being useful in reducing costs/power consumption for consumer CPUs by reducing the number of lanes needed. A 2x 5.0 or 1x 6.0 link would be just fine for any M.2 SSD on the market today, for example.JasonMZW20 - Thursday, May 27, 2021 - link

PCIe 4.0 x4 SSDs could be updated to use PCIe 5.0 x2 lanes and signaling, but they'd still consume the same power without redesigning the SSD controller for PCIe 5.0. CPU I/O might end up using more power to drive faster 5.0 signals too.PCIe 5.0 and 6.0 may also increase development costs of mainboards, as they'll likely need more copper to handle extra bandwidth or redrivers to amplify signals (as we see with 4.0 boards today). If data integrity is an issue, more expensive retimers can be used to retransmit a fresh copy of data to devices that exceed signal loss limits or, as in 6.0, FEC can be used.

I don't expect to see any consumer PCIe 5.0 devices within the next year or two.

vol.2 - Wednesday, July 21, 2021 - link

probably like 5 years + until the industry is lined-up for a shift past 4dotjaz - Tuesday, June 1, 2021 - link

It doesn't reduce power consumption. PAM4 isn't cheap to process.While there might be fewer lanes but they are much higher quality lanes, so likely more expensive.

ct909 - Wednesday, May 26, 2021 - link

No one will ever need more than 640kb of memory.beginner99 - Wednesday, May 26, 2021 - link

He didn't say never just that right now it isn't useful for getting better performance. Even a RTX 3090 isn't limited by pcie 3.0x16. For consumers the network limit is the internet connection. hence why 1gbe is still essentially the standard as barley anyone needs more due to internet speed limits and data caps.I agree FatFlatulentGit that it can help with having to provide less lanes of a higher version. Plus pcie4 to the pch is IMHO the big benefit of rocket lake. But even then in real-world it probably doesn't add much value as few people are coping files from ssd to ssd on regular basis.

Sadly due to "good enough" we will see consumer and server hardware drift further apart again. race to bottom on consumer side. Bad for us enthusiast as it will make new great tech far more expensive. Just look at 10gbe.

fallaha56 - Wednesday, May 26, 2021 - link

@beginner not true, there are already PCIe bottlenecked scenarios eg emulationthere are also applications that will work far better with higher bi-directional bandwidth eg video editing / transcoding