TSMC Boosts CapEx by $1 Billion, Expects N5 Node to Be Major Success

by Anton Shilov on January 22, 2020 11:15 AM EST

TSMC is on track to begin high-volume production of chips using its 5 nm technology in the coming months, the company said in its conference call last week. While so far the number of 5 nm tape-outs is lower when compared to the number of 7 nm tape-outs several months before production start, TSMC expects the process to become a major commercial success. Meanwhile, to ensure that it has no production constraints, the company plans to increase its 2020 CapEx by $1 billion.

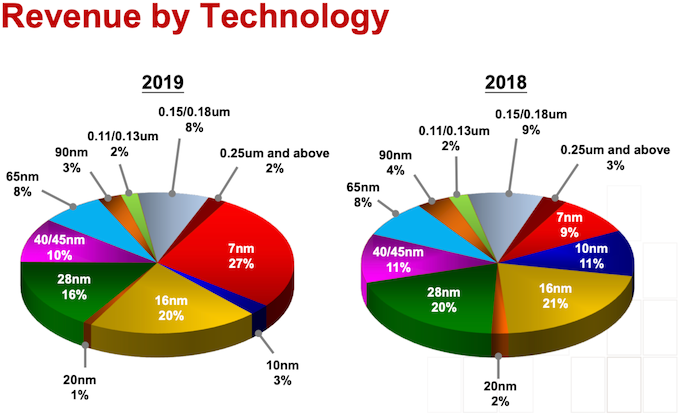

It is well known that TSMC’s N5 manufacturing technology provides substantial improvements over the company’s N7 fabrication process (1.8x higher transistor density, +15% frequency or -20% power consumption), so major customers of the company are more than inclined to adopt it. TSMC is on track to start high volume manufacturing (HVM) using the technology in the first half of this year. So far, the number of N5 tape-outs is lower when compared to the number of N7 tape-outs at the same stage of development (i.e., several months before HVM) becase alpha customers have taped out a slightly lower number of N5 designs and other clients are yet to catch up. Meanwhile, TSMC remains optimistic about the technology’s ramp and expects N5 revenue to account for 10% of its 2020 wafer sales revenue, which essentially means that business performance of N5 in its first year will be the same as business performance of N7 in its first year.

There are several reasons why TSMC’s N7 node turned out to be a huge commercial success for the foundry. First up, most of its customers skipped the 10 nm node and were more than motivated to go with 7 nm. Secondly, TSMC did not have a strong competition with its N7 technology: GlobalFoundries pulled out of the 7 nm race, whereas Samsung Foundry hardly processed any significant number of wafers using its 7LPP process. Thirdly, because N7 is a considerably more complex technology than TSMC’s 16 nm or 10 nm nodes, the company charges more money per wafer than before, which drives a greater revenue share for the process.

C. C. Wei, Vice Chairman and CEO of TSMC said the following:

“The 5 nm tape-out is little bit less than 7 nm compared at the same stage of the time. However, the most important thing is that the high-volume tape-out is almost equal. So, we expect that our 5 nm ramp is a very fast and smooth and it will contribute about 10% to this year's revenue."

Since TSMC’s N7 is considered as a long-living node, demand for the process is not expected to drop radically when N5 enters HVM, as there are tens of fabless semiconductor developers waiting to produce their 7 nm designs. Apparently, to satisfy demand for chips made using TSMC’s N7, N7+, N7P, N6, N5, and N5P manufacturing technologies (and offer some additional capacity for specialty processes as well as for advanced packaging), the company will have to further increase its 2020 CapEx by a billion of dollars up from $14 billion - $15 billion estimated last year.

TSMC does not say exactly how the additional $1 billion will be spent, but since in the coming quarters it will be ramping production using four process technologies that that use extreme ultraviolet lithography (EUVL) for select layers (up to 14 layers in case of N5, up from 4 and 5 in case of N7+ and N6) and multipatterning for some others, it is likely that the foundry is going to need some additional leading-edge equipment.

Wendell Huang, VP and CFO of TSMC, said the following:

“Other than the advanced technology, we also mentioned earlier, we also increased the CapEx this year for specialty technology as well as advanced packaging. So those are the areas that we are focusing on.”

Related Reading:

- TSMC: 5nm on Track for Q2 2020 HVM, Will Ramp Faster Than 7nm

- TSMC Radically Boosts CapEx to Expand Production Capacities, To Reach $14B For 2019

- Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020

- TSMC: N7+ EUV Process Technology in High Volume, 6nm (N6) Coming Soon

Source: TSMC

40 Comments

View All Comments

Teckk - Wednesday, January 22, 2020 - link

Anton, does TSMC not only Fab but also have the Assembly/Test piece of the flow as well? E.g. Apple or AMD (ones not dependent on GF I/O dies) gets the complete package out of TSMC?Also "advanced technology" and "specialty technology" haha that's good.

s.yu - Wednesday, January 22, 2020 - link

IIRC 2 years ago TSMC was expected to maintain the lead until 5nm, after which Samsung might gain an advantage with 3nm and GAA.Curiousland - Wednesday, January 22, 2020 - link

In the very recent Taiwanese local news I read, the site for 3nm fab in Tainan Science Park is under construction (with pictures). Local government is also helping acquiring more lands for the Park ready for 2nm fab. So who will win the 3-nm battle is yet to be determined. Note not like samsung, TSMC is usually keeping lower profile and won't say too much till they are confidence and with concrete plan for HVM.ksec - Thursday, January 23, 2020 - link

And we are now pretty sure GAA wont be ready for 3nm in volume. So it looks like Samsung made the wrong bet yet again.s.yu - Thursday, January 23, 2020 - link

Yeah, I said might, I don't have that much confidence in Samsung either.Hulk - Wednesday, January 22, 2020 - link

I realize the feature size between TSMC and Intel is not really comparable at 14nm, 10nm, etc. but how did Intel fall so far behind. They seem to be struggling (still) with 10nm while TSMC is moving to 5nm? Who would have thought it 10 years ago? Is Intel really as far behind in process technology as it seems to someone not really keen on this business?ET - Wednesday, January 22, 2020 - link

Yes, but Intel is still promising 7nm for 2021. Let's see how that turns out. Intel 10nm should be around TSMC's 7nm and Intel's 7nm should be like TSMC's 5nm. Which still means that Intel is behind in any case, but it still has a chance to at least get on more or less equal footing. Though at this point I don't really trust Intel projections.Toadster - Wednesday, January 22, 2020 - link

it's always interesting to read "Intel 10nm should be around TSMC's 7nm and Intel's 7nm should be like TSMC's 5nm" - how can one number be like a different one? what qualifies the difference in measurement, and shouldn't the measurement be the reported #? 10<> 7 and 7 <> 5boeush - Wednesday, January 22, 2020 - link

The numbers used have lost any relation to any real physical dimensions of the actual circuitry. At this pace, soon (in ~10 years) we will be at subatomic sizes, which obviously will be even more manifestly meaningless. Chalk it up to marketing "genius"...flgt - Wednesday, January 22, 2020 - link

It’s probably better to look at figures of merit of the transistor structure than any particular gate pitch, ie the frequency/voltage curve. Typically smaller gate pitch led to better FOM’s in the past but now with technologies like FinFET and GAA, two transistors with the same pitch can have widely different performance.