Samsung Announces 3nm GAA MBCFET PDK, Version 0.1

by Dr. Ian Cutress on May 14, 2019 8:00 PM EST- Posted in

- Semiconductors

- Samsung

- 3nm

- GAAFET

- MBCFET

_678x452.jpg)

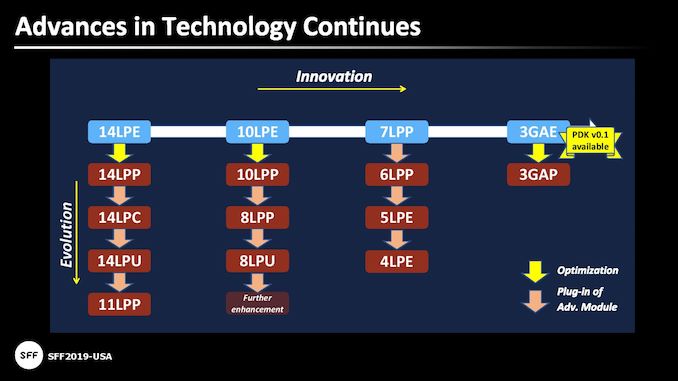

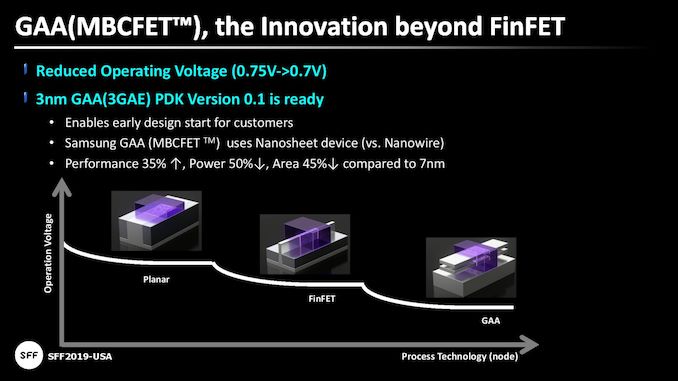

So what comes after 7nm, after 6nm, after 5nm, and after 4nm? That's right: 3nm! At Samsung's Foundry Forum event today, Samsung has announced that the first alpha version of its Product Design Kit for its first 3nm process is now ready for customers. What makes this announcement special is that 3nm is the intersection point where Samsung intends to introduce the next generation of Gate-All-Around (GAA) technology that will replace FinFETs.

Beyond the FinFET: Moving to Gate-All-Around

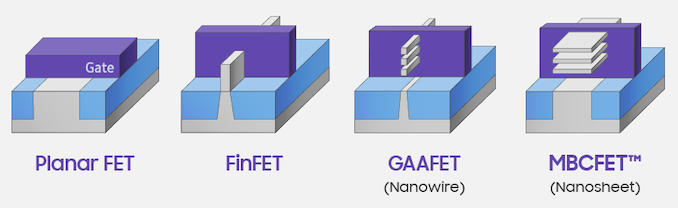

The main driver for innovation in logic-based process technologies over the past decade has been FinFETs. Compared to a standard planar transistor, the FinFET allowed for better performance and voltage scaling as the process node decreased, minimizing the negative aspects of transistor limitations. FinFETs work by increasing the contact area between the channel of the transistor and the gate by scaling in a vertical direction, allowing for faster switching times and higher current density compared to a planar design.

However, like planar transistors, FinFET transistors eventually reach a point where they cannot scale as process nodes shrink. In order to scale, that contact area between the channel and the gate needs to increase, and the way to do this is to use a Gate-All-Around (GAA) design. GAA adjusts the dimensions of the transistor to ensure that the gate is also below the channel, not only on the top and the sides. This allows a GAA design to stack transistors vertically, rather than laterally.

GAA based FETs (GAAFETs) can come in a variety of form factors. Most of the research has pointed to nanowire based GAAFETs, with a small channel width and making the channel as small as possible. These type of GAAFETs are typically useful for low power designs, but are hard to manufacture. The other implementation is making the channel like a horizontal sheet, increasing the volume of the channel, which affords benefits towards performance and scaling. This nano-sheet based GAAFET is what Samsung is calling a Multi-Bridge Channel FET, or MBCFET, which is going to be a trademarked name for the company.

Where planar transistors scaled to around 22nm/16nm, FinFETs have been ideal as we go down from 22nm/14nm to 5nm and 4nm. Samsung is planning to introduce nano-sheet based GAAFETs on its 3nm design, replacing FinFETs entirely.

Building on 3nm: PDKs

When a semiconductor company designs a new chip on a given process, one of the tools they need is a design kit from the foundry then plan to use. For anyone creating an Arm chip on 14nm chip today for example, they would call up Arm and ask for the Cortex-A55 design kit for Samsung or TSMC or GlobalFoundries, which has been optimized for that process. For 14nm, these design kits are very mature, and Arm is likely to offer different versions depending if you want a high frequency or a low power optimization.

However when a process technology is new, early alpha and beta versions of these product design kits (PDKs) become available. The PDK contains the design rules for the process, as well as optimizations that are used to make the best for power and performance. Typically the foundry will update the PDK as more chips are produced and more variations are tested to help its customers make the best chips.

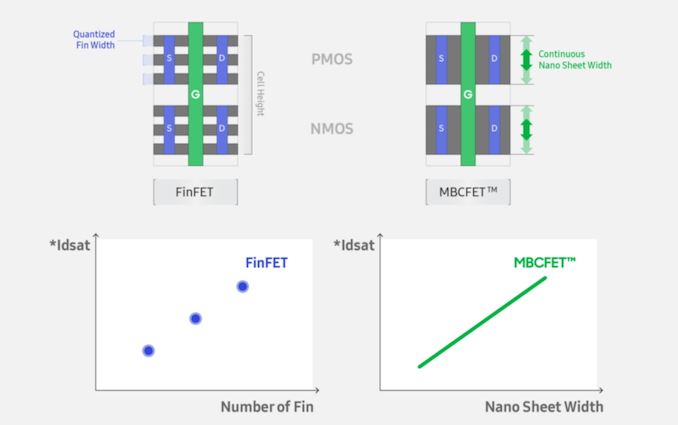

The Nuance with MBCFETs

One of the features of MCBFETs that wasn’t specifically listed in Samsung’s press release is that nano-sheet based FETs are extremely customizable. The width of the nanosheet is a key metric in defining the power and performance characteristics: the higher the width, the higher the performance (at higher power). Samsung has included in its PDK four different nanosheet widths in order to provide co-optimization within the same chip design: transistor designs that focus on low power can use smaller nanosheets, while logic that requires higher performance can go for the wider sheets, but ultimately it's a continuous scale. By contrast, FinFETs only have one power/frequency design point within a process node design for a given fin count, creating only discrete profiles possible.

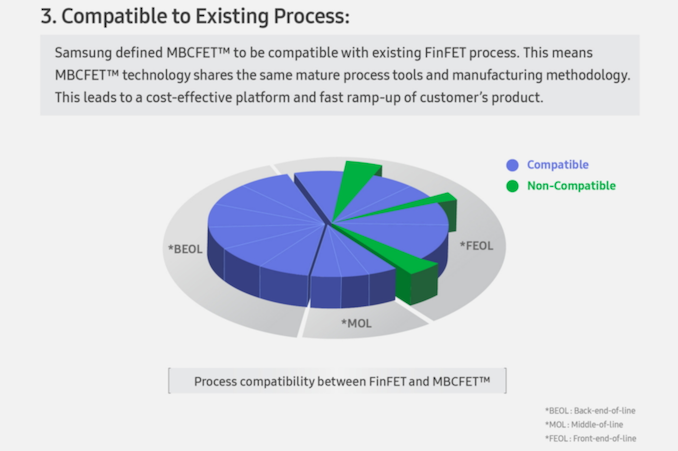

Samsung states that its 3GAE design, regardless of the sheet width design required, will allow for direct IP porting from any of its 4nm family designs. 3GAE and 4LPP share the same BEOL design rules, enabling this.

Samsung Announces 3nm GAA MBCFET PDK, Version 0.1

Today’s announcement is that Samsung is offering its first alpha version of the PDK for its first generation 3nm process that uses MBCFETs. Samsung is calling this process its ‘3GAE’ process, and this alpha version will allow its partners to start getting to grips with some of the new design rules for its 3GAE process.

Samsung is making a lot of promises with its first 3GAE process. One of the headlines is lowering the operating voltage from 0.75 volts to 0.70 volts, which will be a good step in power. The headline PPA values that Samsung is announcing are also impressive: compared to 7nm, 3GAE will offer 1.35x performance, 0.5x power, with a 0.65x die area.

Samsung states that these performance numbers are based on using larger width cells for critical paths where frequency is important, and smaller width cells for non-critical paths where power savings are crucial. Technically Fmax of the widest cells is listed as 1.5x, while power at Fmax is 0.6x. Power at iso-performance is where the 0.5x number comes from.

To put some of this in perspective: Samsung expects its 3GAE process to offer first customer tapeouts in 2020, with risk production in late 2020 and volume manufacturing in late 2021.

Beyond 3GAE, Samsung has already outlined that its second generation 3nm process will be called 3GAP, with a focus on high performance operation. The 3GAP process will be optimization focused, taking advantage of what Samsung has learned from 3GAE. 3GAE will go into risk production in 2021, with mass production likely in 2022.

PDK Tools and EDA Partners

For those that are interested, the PDK tools includes SPICE, DRC, LVS, PEX, P-Cell, Fill Deck, and P&R Techfile. EDA Partners include Cadence, Mentor, and Synopsys.

Related Reading

- Samsung to Invest $115 Billion in Foundry & Chip Businesses by 2030

- Samsung Completes Development of 5nm EUV Process Technology

- Samsung Foundry Roadmap: EUV-Based 7LPP for 2018, 3 nm Incoming

- Samsung Foundry Updates: 8LPU Added, EUVL on Track for HVM in 2019

- Samsung Starts Mass Production of Chips Using Its 7nm EUV Process Tech

32 Comments

View All Comments

name99 - Tuesday, May 14, 2019 - link

Oh Samsung, you really need to hire better marketers.OBVIOUSLY the correct name should have been "Abundant Bridge Channel FET" or abcFET!

More seriously, how plausible is this "variable width" claim? A few years ago I saw similar claims regarding finFET height, and I believe TSMC even created a demo chip showing this. (Here's a patent that sorta covers part of the tech:

https://patents.google.com/patent/US20150262861 )

But as far as I know this possibility has never been exploited in the mainline processes of any fab.

Obviously the geometry is somewhat different, which may make variable width cheaper than variable height. But the fact that Samsung isn't highlighting this makes me wonder if it's the sort of degree of freedom that sounds good in principle, but is not actually that useful in practice?

Ian Cutress - Tuesday, May 14, 2019 - link

They had more detail on it in the afternoon talks. Their PDK comes with four variable width options that are optimized so far, so it's more than just being hopeful. If I can get the slides from the main presentations I'll write something up about it.name99 - Tuesday, May 14, 2019 - link

Perhaps I wasn't clear? The difference is between "continuously variable" and "discretely variable".If you have four discrete widths is that so different from today where you might use two fins for low speed logic and maybe up to five fins (or more) for either high speed or to drive pins?

Is the significant difference that the gradations are substantially smaller than the "per fin" gradations we see today, so that even discrete width differences allow one to optimize slightly closer to the ideal drive current for that particular circuit?

It remains unclear to me if the number of vertical sheets is a second independent variable (so that today's equivalent of coarse steps will be anything from 2 through 5+ sheets, with width providing a fine adjustment to the drive current) or if three sheets (or whatever) is pretty much baked into a particular process and ALL the variation is via the widths.

And how much is this ability to approach the ideal drive current (whether small discrete steps, or continuous variation) worth? 5% in reduced power or 20%?

saratoga4 - Wednesday, May 15, 2019 - link

Continuously variable like planar transistors, so different than the discrete finfet sizes. Should save some area.justaviking - Wednesday, May 15, 2019 - link

"Oh Samsung, you really need to hire better marketers.OBVIOUSLY the correct name should have been "Abundant Bridge Channel FET" or abcFET!"

How about...

Best Optimization for Best All-around FET.... BobaFET

name99 - Wednesday, May 15, 2019 - link

Sir, today you win the internets and my admiration!Rοb - Monday, June 17, 2019 - link

MBCFET is from 2003: https://ieeexplore.ieee.org/document/1264877 - Also, it's BoboFeet: https://static.comicvine.com/uploads/scale_small/0...attila123 - Sunday, January 19, 2020 - link

You're troll and a hater. Are you an engineer? are you a PHD ?? If you are so right why don't you write an academic paper and submit it, if you are so right? 3nm was a major feat. Something people thought was not possible. But they did it. TSMC is just good at FinFit. After that, what? They are better than Samsung at Fin-fit. Samsung went Right into EUV. It was a mistake. But they knew it was going to be that way. Samsung was making stuff for Apple and everybody way before TSMC. Screens, which nobody can make. LCD. Which Taiwan didn't do until they followed the Koreans. Stop being a troll. Just have a positive tone. and Give them credit for doing something extraordinary. I don't know, people like you and your tone man. you can't say things without that tone? It's disgustingattila123 - Sunday, January 19, 2020 - link

Are you suggesting that they didn't do it? usfull in practice, This technology has been around for a long time. They did it. If it was not don right i'm sure all the scientists would have jumped at Samsung. Well we will see. All I know is that Samsung was the first to use EUV right away. Went straight into into. Didn't work out; But it seems it is going in that direction. This new things that they did. In my opinion, it noteworthy. They did it before anyone. I gues like folding phones. Of course it din't work out at first, but why didn't any body else who claimed they had it release their phones? Probably because they get all their display parts from Samsung. There would be no Huawei without Samsung. They could buy it from their cousins at BOA. Go ahead and see how many people buy your phone.trivik12 - Tuesday, May 14, 2019 - link

Wait their S10 Soc was still 8nm(which was supposedly 10nm with some improvements) and so they are planning 7,6,5,4 and 3nm over next 2 years !!!!! Do we know if Note 10 SOC will atleast use 7nm EUV process.