SK Hynix Develops First 16 Gb DDR5-5200 Memory Chip, Demos DDR5 RDIMM

by Anton Shilov on November 15, 2018 7:00 AM EST

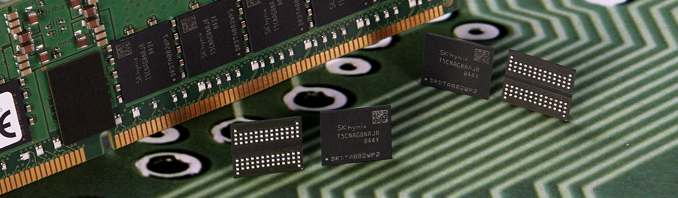

SK Hynix on Thursday announced that it had completed development of its first DDR5 memory chip. The new chip offers a capacity of 16 Gb and is said to be the industry’s first DRAM that is fully compliant with the JEDEC standard, which is yet to be published. Meanwhile, mass production of SK Hynix's DDR5 memory chips is slated for 2020.

The new DDR5 chip from SK Hynix supports a 5200 MT/sec/pin data transfer rate, which is 60% faster than the 3200 MT/s rate officially supported by DDR4. Meanwhile the DRAM operates at 1.1 Volts, a 9% decrease in operating voltage. The monolithic 16 Gb chip is made using SK Hynix’s second generation 10 nm-class process technology (also known as 1Ynm), though the company does not disclose its die size and other peculiarities.

Looking forward, SK Hynix expects its DDR5 lineup to include DRAM chips at 8 Gb, 16 Gb, and 32 Gb capacities, with data transfer rates ranging from 3200 to 6400 MT/s.

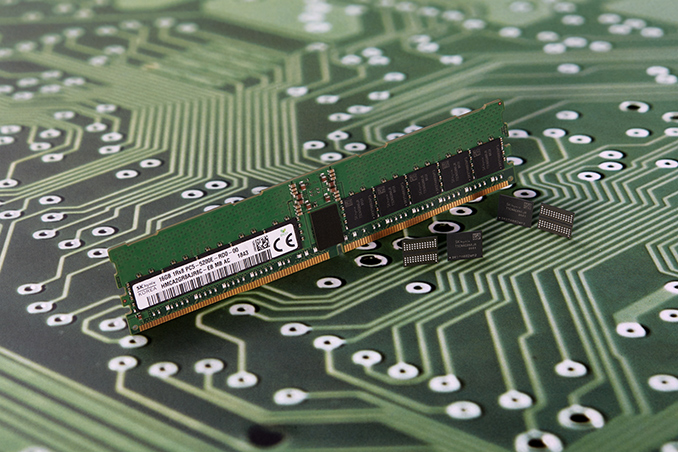

Besides announcing the memory chip, SK Hynix also demonstrated the industry’s first DDR5 Registered DIMM. The DDR5-5200 RDIMM module offers a peak memory bandwidth of 41.6 GB/s, which is in line with DDR4 modules overclocked to their extremes (using LN2-cooled CPUs, etc.). The DDR5 RDIMM itself features 288 pins on a slightly curved edge connector (to reduce the insertion force on every pin), yet its layout and design are a bit different when compared to DDR4 to avoid insertion of DDR5 modules into DDR4 slots and vice versa.

SK Hynix said that it had already shipped DDR5 RDIMMs and UDIMMs to a “major chipset maker” (Intel?) to assist in the development of server and client platforms supporting the new type of memory.

SK Hynix intends to start mass production of DDR5 memory sometimes in 2020, when the aforementioned platforms (at least one of them) are expected to hit the market.

Overall, JEDEC expects DDR5 to bring in I/O speeds ranging from 4266 to 6400 MT/s, with a supply voltage drop to 1.1 V and an allowable fluctuation range of 3% (i.e., at ±0.033V). Along with the performance improvements, the new memory standard also stands to improve in total capacity and DIMM density, with chips planned for 16Gb and beyond.

Under the hood, the new standard will will also bring several major enhancements to the design of memory modules, with the goal of improving their real-world performance and enabling higher data transfer rates. For example, each DDR5 DIMM will feature two independent 32/40-bit channels (without/or with ECC). Furthermore, DDR5 will have a better command bus efficiency (as the channels will have their own 7-bit Address (Add)/Command (Cmd) buses), better refresh schemes, and an increased bank group for extra performance.

Last month Cadence said that enhanced functionality of the standard will enable DDR5 to offer a 36% higher real-world bandwidth vs. DDR4 at the same data transfer rate. While we will not be able to test this claim before 2020, the improvements of DDR5 compared to the predecessor certainly look impressive.

Related Reading:

- Cadence & Micron DDR5 Update: 16 Gb Chips on Track for 2019

- Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019

- JEDEC: DDR5 to Double Bandwidth Over DDR4, NVDIMM-P Specification Due Next Year

Source: SK Hynix

28 Comments

View All Comments

AshlayW - Thursday, November 15, 2018 - link

DDR5 will be a boon for integrated graphics (such as AMD's APU lineup). DDR4 isn't quite fast enough to provide the Raw B/W for these parts to truly replace low-end dGPUs IMHO. DDR5-6400 dual-channel will provide over 100GB/s of raw bandwidth. But even entry-level DDR5 at around 4Gbps would be sufficient combined with arch and compression improvements in these dGPUs.Can't wait for DDR5. :D

AshlayW - Thursday, November 15, 2018 - link

fixing typo: in these iGPUs*tommo1982 - Thursday, November 15, 2018 - link

By the time DDR5 hits consumer market, ZEN 2 APU's should be available. At least I hope AMD will include new DRAM support. There's no reason to continue with DDR4.namechamps - Thursday, November 15, 2018 - link

ZEN 2 is socket compatible with ZEN so little chance that it will have DDR5 support. I mean it is not impossible but AMD would have needed to plan that in the pin configuration for AM4 back in 2016 when AMD was on lifesupport.Maybe Zen 3 in 2021 will use DDR5.

Valantar - Thursday, November 15, 2018 - link

Yep, DDR5 won't come to AMD consumer platforms until past 2020. OTOH, this aligns with the stated start of mass production from this article, so no worries there. Seems like AMD planned this out very well. The part of me dreaming of a new APU-powered HTPC just wants it to arrive yesterday XDSantoval - Friday, November 16, 2018 - link

Assuming AMD will stick to their annual release of CPU generations Zen 3 will be released in 2020 and Zen 4 will be released in 2021. Since Zen 3 will almost certainly be an optimized Zen 2 that will use the same socket, DDR5 will probably have to wait for Zen 4.DanNeely - Thursday, November 15, 2018 - link

It should be a nice boost, otoh IGPUs and bottom end DGPUs will also be growing in size and bandwidth needs. I'd anticipate DDR* versions to remain badly bandwidth constrained for the foreseeable future.Valantar - Thursday, November 15, 2018 - link

While that's true, iGPUs have no real room to grow with DDR4. This could bring them into current AAAs @1080p60 Ultra (or above) territory, which would then likely mean 2020-2021 AAAs at 1080p60 medium-high or so. That sounds pretty dreamy to me.Santoval - Thursday, November 15, 2018 - link

DDR5 will presumably have to wait for Zen 4 CPUs, which are to be released in 2021 at the earliest. Zen 2 based ones next year will not support DDR5, Zen 3 in 2020 will merely be an optimized Zen 2 (and thus it's highly doubtful it will have DDR5 controllers and a new socket), while Zen 4 will be the next new design after Zen 2, with 2021 being long overdue for AMD to replace the current sockets.The above applies to their mainstream and HEDT CPUs. Their server sockets have a zillion pins, many of which are surely reserved for future features (they have extra spare pins to support +32 more cores), so it might be possible to make backwards compatible motherboards with DDR5 support in 2020, with the DDR5 controllers added to the I/O die on the CPU side. The Zen 3 chiplets would probably require only a marginal redesign.

To sum up AMD will introduce DDR5 support in 2021 at the earliest in their Ryzen and TR CPUs and either 2020 or 2021 to their server CPUs.

Alexvrb - Thursday, November 15, 2018 - link

There's no reason they couldn't build a chiplet + I/O design for AM4 that supports DDR4, and use the same chiplets with a different I/O block for AM5. So it isn't IMPOSSIBLE we'll see it prior to Zen 4. I'm not saying they will do this, but from a technical standpoint they could.Also, why would they need to redesign the chiplets? The memory controller is in the I/O block.