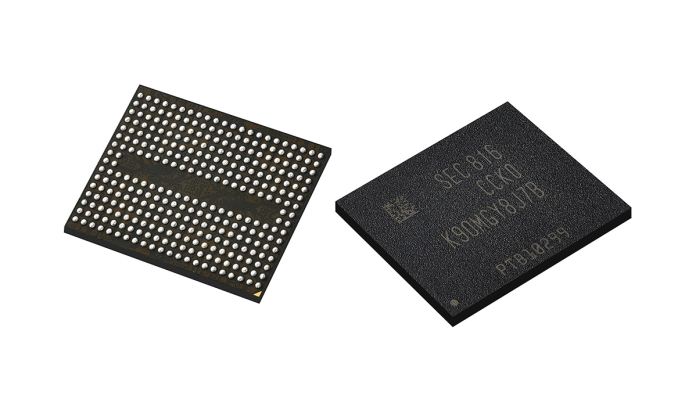

Samsung Begins Mass Production Of 96L 3D NAND

by Billy Tallis on July 9, 2018 11:00 PM EST

Samsung has started mass production of their fifth generation of 3D NAND flash memory, which they brand as V-NAND. This new generation bumps the layer count from 64 up to 96 (officially, "more than 90" layers), providing further density increases without incurring the endurance and reliability costs that came with process shrinks for planar NAND flash memory. Samsung first announced their 96L V-NAND at Flash Memory Summit in August 2017.

The fifth generation V-NAND also includes performance enhancements, most significantly a Toggle DDR 4.0 interface running at 1.4Gbps, compared to the 800Mbps interface speed of Samsung's previous 3D NAND. A reduction of operating voltage from 1.8V to 1.2V offsets the extra power consumption that faster interface speed would otherwise bring. Samsung is also citing improvements to both read and program latency. Read latency did not improve from 48L to 64L, but now has been "significantly" reduced to 50μs. Program (write) latency is down about 30% to 500μs.

Samsung hasn't shared many details about their process refinements, but the height of each memory cell layer has been reduced by 20%, which helps reduce the extremely high aspect ratio of the holes that need to be etched for the vertical strings of memory cells. Difficulties with high aspect ratio etching are widely believed to be the primary cause for delays that Samsung's 48L V-NAND suffered, which led to several product cancellations as Samsung's NAND development failed to keep pace with their SSD controller improvements. Samsung's transition to 64 layers was much smoother, and Samsung is claiming a 30% improvement to manufacturing productivity with the 96L process. Whether this is on a per-bit basis or a per-wafer basis, this should allow for another on-time roll out.

The first 96L part in mass production is a 256Gb TLC (three bits per cell) die, which should see broad usage in the mobile and SSD markets. Larger dies will follow to fulfill the need for higher capacities with lower cost per bit, primarily in the enterprise SSD market. This will include a 1Tb QLC NAND (four bits per cell) part.

Source: Samsung

25 Comments

View All Comments

lilmoe - Tuesday, July 10, 2018 - link

30% better manufacturing productivity... Wonder how much of that will be passed down to the consumer as savings. If it's less than 20%, F U Sammy.ZolaIII - Tuesday, July 10, 2018 - link

Well cost is more dependent on the manufacturing process. If 96 layer brings 25~30% incres in capacity while cell size is down 20% it translates to 1.3x priced 1.5x capacity. 7nm FinFET first generation won't bring any price cut compared to the 10 - 14nm but second generation with denser rooting & EUV will cut the price roughly in half. So by the end of the next year you will have 3x capacity for 1.3x price compared to today advanced 64 layer one's.SiSiX - Tuesday, July 10, 2018 - link

Um, these don't use a 10-14nm, nor are they moving to a 7nm FinFET process. Part of the reason for the stacking in the first place, and the HUGE increase in overall endurance is because they're effectively using "old", very mature process size. (Their "21nm" process node, whatever that works out to be in real world terms.) By and large, Flash memory has more issues the smaller you make the features.piroroadkill - Tuesday, July 10, 2018 - link

It's not such a great idea to shrink flash; the endurance drops off unacceptably. It's why they've gone back to more mature processes and then stacked them in layers. Better density AND reliability.FullmetalTitan - Thursday, July 12, 2018 - link

Pretty sure these 96 layer parts are still on a 22nm architecture, flash doesn't follow the same roadmap as logic. Limitations like extreme aspect ratio etches to form vertical holes for connecting layers are difficult to scale.Samsung IS investing in 1Xnm scale memory technologies, but that will be limited to very high end products probably through the end of the decade.

iwod - Tuesday, July 10, 2018 - link

that is you assuming demand being the sameMrSpadge - Tuesday, July 10, 2018 - link

20% for us, 10% for their margins and future R&D - that's a win-win situation. If they passed the entire cost benefit to us, we'd probably still have to use 1 MBit devices because noone could afford further development.B3an - Tuesday, July 10, 2018 - link

Funny how none of you are thinking about price fixing, just like they undeniably do with RAM. So naive.Ej24 - Tuesday, July 10, 2018 - link

Nand prices haven't really gone up, they've stayed pretty flat for the last year or so, at least judging by consumer ssd prices. Whereas RAM has more than doubled for the same exact product in the same time period. There are also more producers of NAND than RAM with more viable competing designs, 3d, planar, mlc, tlc, and so on. Samsung can't pass on 100% of the savings to you because the initial R&D cost them money upfront and they need to make a profit to keep innovating.iwod - Tuesday, July 10, 2018 - link

You should understand more about market demand and supply before telling others about price fixing and calling other naive.