IDF Fall 2006 - Day 2: Opteron vs. Xeon, SSE4 & Intel's Torrenza competitor Announced

by Anand Shimpi & Virginia Lee on September 27, 2006 1:12 PM EST- Posted in

- Trade Shows

Intel Follows AMD's Lead, Again: Cloning Torrenza

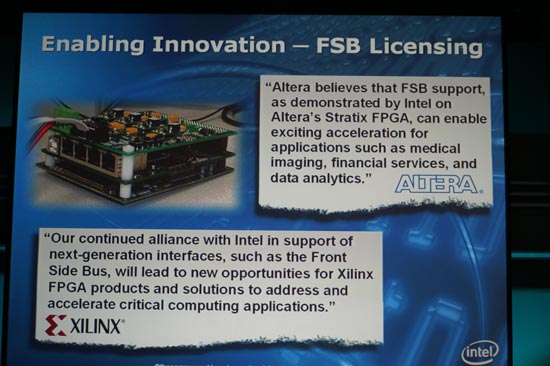

In another example of a string of Intel following AMD's lead, Gelsinger announced extending Intel's FSB license to FPGA manufacturers like Xilinx so that companies can produce other chips that can work alongside Intel processors with a direct FSB connection to the MCH. This should sound a lot like a less elegant implementation of AMD's Torrenza initiative; as you may remember, Torrenza is the platform standard that AMD introduced to allow other, non-AMD processors (or accelerators) to be installed in standard Opteron sockets through licensing and use of the coherent Hyper Transport specification. Intel's FSB licensing will also allow various accelerators to be plugged into a high bandwidth, low latency (potentially cache coherent) bus that would connect directly to the MCH in an Intel system.

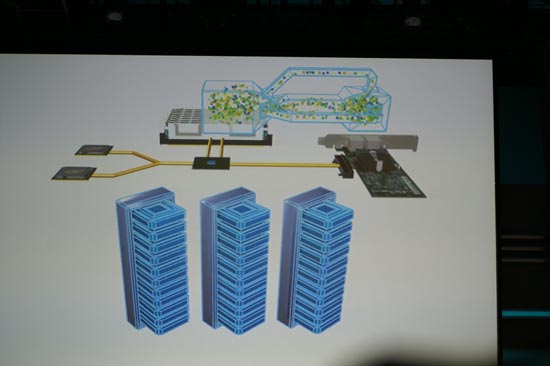

This device somehow implements Intel's FSB license

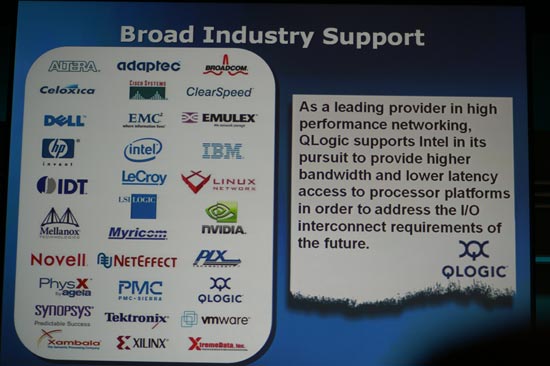

Intel also announced work with IBM to create an extension to PCI Express, codenamed Geneseo that would be used as a higher bandwidth, lower latency interface for everything from graphics cards to physics accelerators. Gelsinger threw up a slide that showcased the broad industry support for creating products that would work with the Geneseo interface. Notable members of the alliance are NVIDIA and AGEIA for its PhysX card, indicating that Intel's thinking is similar to AMD's in that there could be a future for physics accelerator cards or even a higher speed, lower latency interconnect for GPUs that would utilize this interface. Note the absence of ATI from the list of partners supporting Intel's efforts.

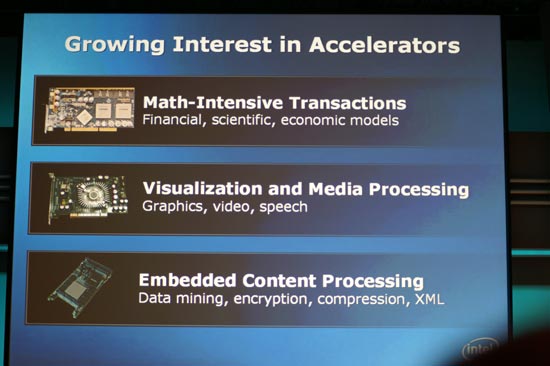

Effectively, what Intel is hoping to do is gain momentum and industry support for an alternative to AMD's Hyper Transport for use with various 3rd party accelerator cards. Since Intel is unlikely to embrace Hyper Transport and AMD's Torrenza's initiative, simply extending PCI Express with additional focus on creating a higher bandwidth, lower latency version of the bus for these accelerator cards with the help of the rest of the industry (except AMD) is the next best option.

Intel expects to iron out a specification in the next 1 - 1.5 years, and the first products will be available in the coming years after that. Obviously, AMD has a much larger head start in this area and we're interested to see how things pan out given AMD's timing advantage and industry support for Hyper Transport.

IBM came on stage to talk about some of the things Intel and IBM focused on in developing the spec for the new Geneseo interface spec for 3rd party accelerators to communicate directly with the MCH in a system. The information that was shared was vague at best, but the animations during the presentation give you an example of a usage model Intel is looking at with its Torrenza-like platform approach.

Based on the vague comments by IBM, it looks like these accelerators running over the Geneseo interface could be cache coherent, support reordering of memory requests in order to prioritize the most important requests and able to be power managed must like any other component in the system.

18 Comments

View All Comments

jiulemoigt - Wednesday, September 27, 2006 - link

Actully it's even funnier than that as all of the 1207 mobo's are dual or multi socket mobos at this point so it is most likely to be a AM2 940 pin 1000 chip or the Op 285 which is a socket 939. Any way you look at that it is questionible which is interesting since I was under the impresion that the core2 were faster than anything amd had even if the mobo chipsets have issues.JarredWalton - Wednesday, September 27, 2006 - link

I'm not sure if Anand already updated this, but both systems were dual socket and it was a "Socket F 2.80 GHz" processor config in the AMD unit, not AM2, Opteron 285, or some other hypothetical config to show Intel in a better light. The benchmark, on the other hand, is a different story as it could be just about anything. :)theteamaqua - Wednesday, September 27, 2006 - link

this company is in big troubleAmpedSilence - Wednesday, September 27, 2006 - link

Based on what?The Core 2 Duo is doing well and trumps AMD64 for the time being. They are releasing a quad-core almost a year before AMD.

What are you using as a basis for this conclusion?

btw, i have three AMD64 machines (one X2 and two AMD64's).

Viditor - Wednesday, September 27, 2006 - link

closer to a half year...at the very most it will be 7 months.

He might be referring to Torrenza. It's probably the most underestimated and misunderstood advancement AMD has announced. Remember that there are already coprocessers that can just drop into an Opteron ssocket, and IBM is already shipping servers with HTX connections. Intel will be another 1-1.5 years before they are ready to do this...and there isn't any idea what kind of support they will end up with at that point.

psychobriggsy - Wednesday, September 27, 2006 - link

Quad-core on two dies, utilising their experience from the Smithfield panic reaction to AMD's X2. However it shows that once Intel gets woken up, they don't go back to sleep after doing 'enough', they'll continue until they have the lead.AMD fell asleep after dual-core, indeed after K8 considering dual-core was meant to be a possibility from day one. It is costing them now, apart from their platform work which is still ahead. I think AMD should have investigated dual-die MCMs for quad-core, instead 4x4 is a reactionary hack solution (that'll work nevertheless, and it'll have good memory bandwidth).

Calin - Thursday, September 28, 2006 - link

AMD would better ramp the 65nm technology as soon as possible - only after that, quad cores will become a real/profitable possibilityPirks - Wednesday, September 27, 2006 - link

he's using some green smelly stuff as his basis, isn't that obvious ;))