IBM Z

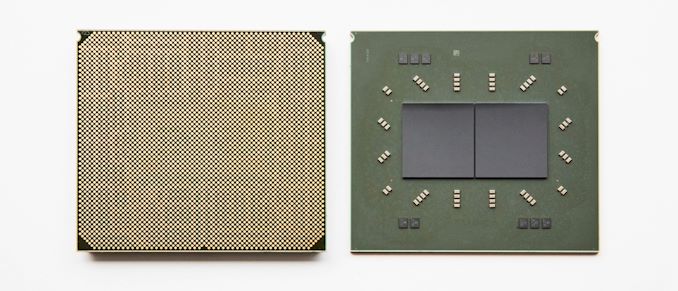

At Hot Chips last week, IBM announced its new mainframe Z processor. It’s a big interesting piece of kit that I want to do a wider piece on at some point, but there was one feature of that core design that I want to pluck out and focus on specifically. IBM Z is known for having big L3 caches, backed with a separate global L4 cache chip that operates as a cache between multiple sockets of processors – with the new Telum chip, IBM has done away with that – there’s no L4, but interestingly enough, there’s no L3 either. What they’ve done instead might be an indication of the future of on-chip cache design.

Hot Chips 2021 Live Blog: CPUs (Alder Lake, Zen3, IBM Z, Sapphire Rapids)

Welcome to Hot Chips! This is the annual conference all about the latest, greatest, and upcoming big silicon that gets us all excited. Stay tuned during Monday and Tuesday...

39 by Dr. Ian Cutress on 8/23/2021IBM to use Samsung 7nm EUV for Next-Gen POWER and z CPUs

IBM has announced it has signed an agreement with Samsung Foundry to produce its next-generation processors. This includes processors for IBM Power Systems, IBM z, and LinuxONE systems, all...

24 by Anton Shilov on 12/21/2018