CXL

The CXL consortium has had a regular presence at FMS (which rechristened itself from 'Flash Memory Summit' to the 'Future of Memory and Storage' this year). Back at FMS 2022, the company had announced v3.0 of the CXL specifications. This was followed by CXL 3.1's introduction at Supercomputing 2023. Having started off as a host to device interconnect standard, it had slowly subsumed other competing standards such as OpenCAPI and Gen-Z. As a result, the specifications started to encompass a wide variety of use-cases by building a protocol on top of the the ubiquitous PCIe expansion bus. The CXL consortium comprises of heavyweights such as AMD and Intel, as well as a large number of startup companies attempting to play in different segments on...

Samsung Unveils CXL Memory Module Box: Up to 16 TB at 60 GB/s

Composable disaggregated data center infrastructure promises to change the way data centers for modern workloads are built. However, to fully realize the potential of new technologies, such as CXL...

17 by Anton Shilov on 4/3/2024Samsung, MemVerge, and H3 Build 2TB CXL Memory Pool

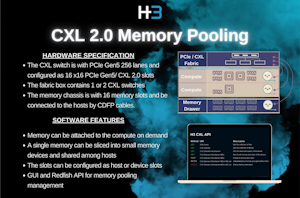

Samsung, MemVerge, H3 Platform, and XConn have jointly unveiled their 2 TB Pooled CXL Memory System at the Flash Memory Summit. The device can be connected to up to...

4 by Anton Shilov on 8/14/2023Micron's CZ120 CXL Memory Expansion Modules Unveiled: 128GB and 256GB

This week, Micron announced the sample availability of its first CXL 2.0 memory expansion modules for servers that promise easy and cheap DRAM subsystem expansions. Modern server platforms from...

7 by Anton Shilov on 8/9/2023Next-Generation CAMM, MR-DIMM Memory Modules Show Up at Computex

Dynamic random access memory is an indispensable part of all computers, and requirements for DRAM — such as performance, power, density, and physical implementation — tend to change now...

4 by Anton Shilov on 6/2/2023Compute Express Link (CXL) 3.0 Announced: Doubled Speeds and Flexible Fabrics

While it’s technically still the new kid on the block, the Compute Express Link (CXL) standard for host-to-device connectivity has quickly taken hold in the server market. Designed to...

4 by Ryan Smith on 8/2/2022OpenCAPI to Fold into CXL - CXL Set to Become Dominant CPU Interconnect Standard

With the 2022 Flash Memory Summit taking place this week, not only is there a slew of solid-state storage announcements in the pipe over the coming days, but the...

8 by Ryan Smith on 8/1/2022Using a PCIe Slot to Install DRAM: New Samsung CXL.mem Expansion Module

In the computing industry, we’ve lived with PCIe as a standard for a long time. It is used to add any additional features to a system: graphics, storage, USB...

47 by Dr. Ian Cutress on 5/11/2021Micron Abandons 3D XPoint Memory Technology

In a sudden but perhaps not too surprising announcement, Micron has stated that they are ceasing all R&D of 3D XPoint memory technology. Intel and Micron co-developed 3D XPoint...

60 by Billy Tallis on 3/16/2021Microchip Announces PCIe 5.0 And CXL Retimers

Microchip is entering the market for PCIe retimer chips with a pair of new retimers supporting PCIe 5.0's 32GT/s link speed. The new XpressConnect RTM-C 8xG5 and 16xG5 chips...

8 by Billy Tallis on 11/11/2020Compute eXpress Link 2.0 (CXL 2.0) Finalized: Switching, PMEM, Security

One of the more exciting connectivity standards over the past year has been CXL. Built upon a PCIe physical foundation, CXL is a connectivity standard designed to handle much...

5 by Dr. Ian Cutress on 11/10/2020Rambus Unveils PCIe 5.0 Controller & PHY

Rambus has developed a comprehensive PCIe 5.0 and CXL interface solution for chips built using 7 nm process technologies. The interface is now available for licensing by SoC designers...

17 by Anton Shilov on 11/13/2019Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Synopsys, one of the leading developers of chip development tools and silicon IP, demonstrated its CXL over PCIe 5.0 as well as CCIX 1.1 over PCIe 5.0 solutions at...

5 by Anton Shilov on 10/11/2019CXL Consortium Formally Incorporated, Gets New Board Members & CXL 1.1 Specification

Over four years ago, Intel started to develop what is now known as Compute Express Link (CXL), an interface to coherently connect CPUs to all types of other compute...

5 by Anton Shilov on 9/20/2019Arm Joins CXL Consortium

Arm has officially joined the Compute Express Link (CXL) Consortium in a bid to enable its customers to implement the new CPU-to-Device interconnect and contribute to the specification. Arm...

7 by Anton Shilov on 9/13/2019AMD Joins CXL Consortium: Playing in All The Interconnects

AMD's CTO, Mark Papermaster, has published a blog post this week said that AMD has joined the Compute Express Link (CXL) Consortium. The industry group is led by a...

43 by Anton Shilov on 7/19/2019Compute Express Link (CXL): From Nine Members to Thirty Three

Last month the CXL Specification 1.0 was released as a future cache coherent interconnect that uses the PCIe 5.0 physical infrastructure but aimed to provide a breakthrough in utility...

18 by Dr. Ian Cutress on 4/15/2019Intel Agilex: 10nm FPGAs with PCIe 5.0, DDR5, and CXL

Ever since Intel purchased Altera for an enormous amount of money a few years ago (ed: $16.7B), the FPGA portfolio that has been coming out has largely been a...

12 by Ian Cutress on 4/2/2019CXL Specification 1.0 Released: New Industry High-Speed Interconnect From Intel

With the battleground moving from single core performance to multi-core acceleration, a new war is being fought with how data is moved around between different compute resources. The Interconnect...

48 by Ian Cutress on 3/11/2019