The new Opteron 6300: Finally Tested!

by Johan De Gelas on February 20, 2013 12:03 AM ESTMeasuring Real-World Power Consumption

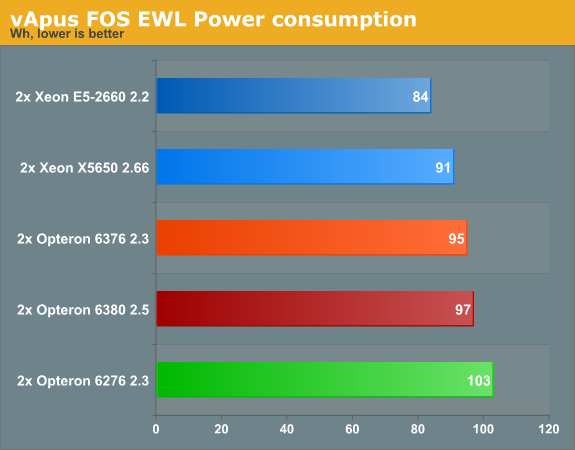

The Equal Workload (EWL) version of vApus FOS is very similar to our previous vApus Mark II "Real-world Power" test. To create a real-world “equal workload” scenario, we throttle the number of users in each VM to a point where you typically get somewhere between 20% and 80% CPU load on a modern dual CPU server. The amount of requests is the same for each system, hence "equal workload".

The CPU load is typically around 30-50%, with peaks up to 65% (for more info see here). At the end of the test, we get to a low 10%, which is ideal for the machine to boost to higher CPU clocks (Turbo) and race to idle. We use the "Balanced" power policy and enable C-states as the current ESXi settings make poor use of the C6 capabilities of the latest Opterons and Xeons.

We cannot say "mission accomplished", but AMD has made significant progress. 12% to 20% better performance while decreasing the power consumption by 6% to 8% is pretty good. The 95W TDP Xeons are still the performance per Watt champs though. Still, it looks like the Opteron is a decent alternative for some. Power consumption is about 12-13% higher (6376 vs E5-2660), but the performance per dollar is slightly better.

55 Comments

View All Comments

sherlockwing - Wednesday, February 20, 2013 - link

These Piledriver based Opterons look competitive but the threat of Ivy-EP is immenient. The last time Intel die-shrunk their High end platform they introduced the monsterous 10 core Westmere-EP(the current Xeon E7 lineup), I wouldn't be surprised Ivy-EP introduces 10/12 core extreme E7 Xeons as well as Octa Xeons with better performance/watt.Kevin G - Wednesday, February 20, 2013 - link

Ivy Bridge-E is indeed coming but it is looking to be 6 months out. These Opterons were shipping since November which would give them a 10 month lead time. The real question for AMD is what they'll have in response in that time frame. Steamroller based parts all look to be released in 2014. On the bright side, AMD should be pairing those chips with a new socket as DDR4 becomes available.One thing though about Ivy Bridge-E is that it will also be a socket 2011 part so migration to it should get relatively quick in comparison to the Westmere-EP to Sandybridge-E transition. The same cost savings for OEM noted in this article for socket G32 Opterons will apply to Ivy Bridge-E this time around.

Oskars Apša - Wednesday, February 20, 2013 - link

Wasn't intels 2011 socket to be only physically identical, but electrically totally redesigned?Hrel - Friday, February 22, 2013 - link

"These Opterons were shipping since November"I reject this statement. Nothing counts as being "on the market" until Anandtech has done a full review of it. That's my stance and I'm sticking to it :P

Beenthere - Wednesday, February 20, 2013 - link

...is that the 63xx series is focused primarily on micro servers where it fits well. If the just disclosed Jaguar cores are any indication of AMD products to be released this and next year, I'd say AMD is back in the game in many PC and portable markets.The only thing Ivy Bridge has going for it is reduced power but at a price penalty.

JohanAnandtech - Thursday, February 21, 2013 - link

SeaMicro was indeed one of first to use Piledriver based cores, but I don't think the Opteron 6300 is meant to be a "typical" microserver CPU. Otherwise, AMD would have focused more on low power parts. This meant to be an update for the general server market.Jovec - Wednesday, February 20, 2013 - link

... as it is showing the multi-threaded chart instead.JohanAnandtech - Wednesday, February 20, 2013 - link

Fixed. Thanks for pointing it out, always appreciated.Death666Angel - Wednesday, February 20, 2013 - link

Hey!I get a " Page Not Found" error from the Racktivity PDU link. :)

ssj3gohan - Wednesday, February 20, 2013 - link

You say that AMDs bad implementation of C6 costs them in the energy efficiency tests, but AFAIK with a low of still 10% CPU the CPU should not enter ACPI C3 (Intel C6), it will probably stay in C1e providing there is still more than enough workload to do on each OS tick.If the xeons are observed to go into ACPI C3, then that is very probably a scheduler optimization specific for intel processors, not an actual implementation problem by AMD. Balancing C-state transitions - especially complete core sleep modes like ACPI C3 - is a notoriously hard task to do because each transition also costs a certain amount of mJ that, on immediate wake, are wasted compared to just leaving the cores in C1(e)